RISC-V ISA介绍

RISC-V ISA

开源

ISA(Instruction Set Architecture)指令集架构

底层硬件电路面向上层软件程序提供的一层接口规范

操作系统提供给应用程序的接口就是系统调用,操作系统和硬件直接就是ISA 硬件部分的话业界里一般叫微架构microarchitecture,有了ISA的抽象层我们做底层开发就不需要关心微架构具体是什么样的

他是一套标准,类似c语言的标准,POSIX标准等等,具体的实现有很多种,不同的cpu厂家实现是不一样的,就比如说x86架构的标准可能由intel和amd等公司来实现

小故事:amd64架构

当年intel先推出64位架构(IA-64)处理器但是他不兼容32位架构的机器,导致芯片滞销,amd后推出64位指令集架构amd64兼容了之前32位指令集,畅销后,软件生态上就占领了先机,intel只能用amd64架构(好像是买amd64的授权,

涉及到授权关系就挺混乱了。。。),intel在此基础上进行了扩充,叫x86-64

ISA定义了

- 基本数据类型

- 寄存器

- 指令

- 内存模型

- 寻址模式

- 异常或中断的处理方式等等

一个比较错误的认为就是

ISA就是汇编,汇编是ISA的一小部分

RISC-V ISA 命名格式

RV[###][abc…..xyz]

- RV:用于标识 RISC-V 体系架构的前缀,即 RISC-V的缩写。

- [###]:{32, 64, 128} 用于标识处理器的字宽,也就是处理器的寄存器的宽度(单位为bit)

- [abc…xyz]:标识该处理器支持的指令集模块集合

模块化ISA

由1个基本整数指令集 + 多个可选的扩展指令集组成。基础指令集是固定的

WC,可定制化芯片

| 基本指令集 | 描述 |

|---|---|

| RV32I | 32位整数指令集 |

| RV32E | RV32I 的子集,用于小型的嵌入式场景 |

| RV64I | 64 位整数指令集,兼容 RV32I |

| RV128I | 128 位整数指令集,兼容 RV64I和RV32I |

| 扩展指令集 | 描述 |

|---|---|

| M拓展 | 提供乘法和除法指令 |

| A拓展 | 提供原子操作指令 |

| F拓展 | 提供单精度浮点数操作指令 |

| D拓展 | 提供双精度浮点数操作指令 |

| C拓展 | 提供压缩指令集 |

| Z拓展 | 提供对控制和状态寄存器(CSR)的操作指令 |

| P拓展 | 提供向量操作指令 |

| B拓展 | 提供位操作指令 |

| 等等 | 等等 |

IMAFD被称为通用(General)组合,用G表示

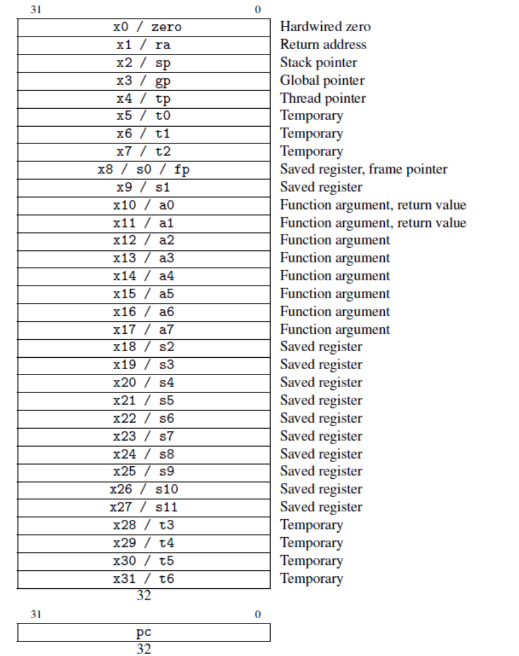

RISC-V通用寄存器

RV32E 将 32 个通用寄存器缩减为 16 个

Hart

HART = HARdware Thread

类似于intel的超线程技术,一个核里可以跑两个线程(指令执行流),这里的HART概念就是这样一条指令执行流

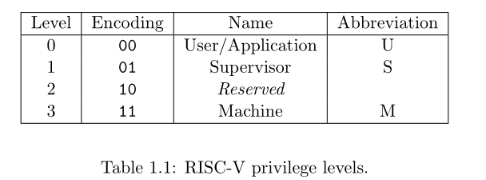

特权级别

level3 machine是最高态

比如说linux操作系统用户态riscv cpu是工作在User(00)级的,内核态cpu是在Supervisor(01)级的

Machine态类似于x86的实模式,上电之后是处于Machine态的,都是物理地址

Control and Status Registers(CSR)

不同的特权级别下时分别对应各自的一套CSR

高级别的特权级下可以访问低级别的CSR,反之不行